# Lecture Notes in Computer Science

Edited by G. Goos, J. Hartmanis, and J. van Leeuwen

2318

# Springer Berlin

Berlin Heidelberg New York Barcelona Hong Kong London Milan Paris Tokyo

# Model Checking Software

9th International SPIN Workshop Grenoble, France, April 11-13, 2002 Proceedings

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

Volume Editors

Dragan Bošnački Eindhoven University of Technology Faculty of Mathematics and Computer Science P.O. Box 513, 5600 MB Eindhoven, The Netherlands

E-mail: dragan@win.tue.nl

Stefan Leue

Albert-Ludwigs-University Freiburg Institute for Computer Science Georges-Koehler-Allee Geb. 051, 79199 Freiburg, Germany E-mail: leue@uni-freiburg.de

Cataloging-in-Publication Data applied for

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

Model checking software: proceedings / 9th International SPIN Workshop, Grenoble, France, April 11 - 13, 2002. Dragan Bošnački; Stefan Leue (ed.). - Berlin; Heidelberg; New York; Barcelona; Hong Kong; London; Milan; Paris; Tokyo: Springer, 2002 (Lecture notes in computer science; Vol. 2318) ISBN 3-540-43477-1

CR Subject Classification (1998): F.3, D.2.4, D.3.1

ISSN 0302-9743 ISBN 3-540-43477-1 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag Berlin Heidelberg New York a member of BertelsmannSpringer Science+Business Media GmbH

http://www.springer.de

© Springer-Verlag Berlin Heidelberg 2002 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Olgun Computergrafik Printed on acid-free paper SPIN 10846644 06/3142 5 4 3 2 1 0

#### Preface

The SPIN workshop series brings together researchers and practitioners interested in explicit state model checking technology as it is applied to the verification of software systems.

Since 1995, when the SPIN workshop series was instigated, SPIN workshops have been held on an annual basis at Montréal (1995), New Brunswick (1996), Enschede (1997), Paris (1998), Trento (1999), Toulouse (1999), Stanford (2000), and Toronto (2001). While the first SPIN workshop was a stand-alone event, later workshops have been organized as more or less closely affiliated events with larger conferences, in particular with CAV (1996), TACAS (1997), FORTE/PSTV (1998), FLOC (1999), World Congress on Formal Methods (1999), FMOODS (2000), and ICSE (2001). This year, SPIN 2002 was held as a satellite event of ETAPS 2002, the European Joint Conferences on Theory and Practice of Software. The co-location of SPIN workshops with conferences has proven to be very successful and has helped to disseminate SPIN model checking technology to wider audiences. Since 1999, the proceedings of the SPIN workshops have appeared in Springer-Verlag's "Lecture Notes in Computer Science" series.

The history of successful SPIN workshops is evidence for the maturing of model checking technology, not only in the hardware domain, but increasingly also in the software area. While in earlier years algorithms and tool development around the SPIN model checker<sup>1</sup> were the focus of this workshop series, the scope has recently widened to include more general approaches to software model checking. Current research in this area concentrates not so much on completely verifying system models, but rather on analyzing source code in order to discover software faults. The state space sizes that this analysis has to cope with require building adequate abstractions as well as algorithmic optimizations, which is reflected in a number of papers presented at SPIN 2002.

Out of the 20 research papers submitted, 10 were selected by the program committee. Every paper received three reviews. The reviewing and acceptance decision making for a submitted research paper for which one of the editors of this volume was a co-author was handled by a sub-committee chaired by Moshe Vardi. A further 3 out of the 20 submitted papers were accepted as extended abstracts in the "work in progress" category which was introduced to give emerging research ideas an opportunity for presentation. One submitted research paper was accepted as a tool demonstration. All three submitted tool presentations were accepted in that category. One tutorial was submitted, and it was also accepted in the tutorial category.

In addition to the selected technical program, SPIN 2002 featured two invited presentations. Edmund M. Clarke (Carnegie-Mellon University), one of the founding fathers of model checking technology, presented work on the use of SAT

<sup>&</sup>lt;sup>1</sup> Freely available on the web from

http://netlib.bell-labs.com/netlib/spin/whatispin.html.

#### VI Preface

solvers in the context of counterexample guided abstraction refinement. Patrick Cousot (ENS Paris), who pioneered research on abstract interpretation, talked about theory and practice of abstract interpretation. For the first time a SPIN workshop offered an invited beginners' tutorial aimed at teaching participants a) how to write models, and b) how to write models that can be efficiently analyzed by the SPIN model checker. This tutorial was given by Theo Ruys (University of Twente) and was open to all ETAPS 2002 participants.

Since overcoming barriers between academia and industry is essential to the advancement of model checking science and technology, industrial usage reports were invited for presentation, as in previous years, and included as extended abstracts into this proceedings volume. Cindy Eisner (IBM) and Doron Peled (University of Texas) presented a comparison of the use of symbolic and explicit model checking techniques in an industrial application environment. Per Bjesse (Prover Technology) discussed perspectives for and limitations of the industrial use of SAT-based model checking techniques. Finally, Yves-Marie Quemener (France Telecom) illustrated the use of model checking technology in the generation of test cases for XML-based telecommunications equipment.

Acknowledgements. The volume editors wish to thank all members of the program committee as well as the external reviewers for their tremendous effort which led to the selection of this year's program. We furthermore wish to thank ETAPS 2002 for inviting us to hold SPIN 2002 as a satellite event. Our particular appreciation goes to Susanne Graf, who acted as our liaison to ETAPS 2002, for accommodating the needs of SPIN 2002. Finally, we wish to thank METAFrame Technologies GmbH for allowing us to use their Conference Online Service system free of charge.

April 2002 Dragan Bošnački Stefan Leue

# Organization

SPIN 2002 was held in cooperation with ACM SIGPLAN as a satellite event of ETAPS 2002, the European Joint Conferences on Theory and Practice of Software, which was organized by the Laboratoire Verimag, Grenoble, France.

## Organizing Committee

Program Chair: Stefan Leue (Albert-Ludwigs-University Freiburg, D)

Organizing Chair: Dragan Bošnački (Eindhoven University of Technology, NL)

## Advisory Committee

Gerard Holzmann (Bell Labs, USA, chair) Amir Pnueli (Weizmann, IL)

## **Steering Committee**

Matt Dwyer (Kansas State, USA)

Stefan Leue (Freiburg, D)

Moshe Vardi (Rice, USA, chair)

Pierre Wolper (Liège, B)

## Program Committee

Dragan Bošnački (Eindhoven, NL, organization chair)

Ed Brinksma (Twente, NL)

Marsha Chechik (Toronto, CA)

Dennis Dams (Bell Labs, USA and Eindhoven, NL)

Rob Gerth (Intel, USA)

Susanne Graf (Verimag, F)

John Hatcliff (Kansas State, USA)

Klaus Havelund (NASA Ames, USA)

Gerard Holzmann (Bell Labs, USA)

Bengt Jonsson (Uppsala, S)

Stefan Leue (Freiburg, D, chair)

Doron Peled (Austin, USA)

Sriram Rajamani (Microsoft Research, USA)

Riccardo Sisto (Torino, I)

Moshe Vardi (Rice, USA)

Willem Visser (NASA Ames, USA)

Pierre Wolper (Liège, B)

#### Referees

Victor Bos Leszek Holenderski Corina Mitrohin Stefan Edelkamp Angelika Mader Theo Ruys

# **Table of Contents**

| Invited Talks                                                                                                                |                |

|------------------------------------------------------------------------------------------------------------------------------|----------------|

| SAT-Based Counterexample Guided Abstraction Refinement                                                                       | 1              |

| Abstract Interpretation: Theory and Practice                                                                                 | 2              |

| Invited Tutorial                                                                                                             |                |

| SPIN Tutorial: How to Become a SPIN Doctor                                                                                   | 6              |

| Tutorial                                                                                                                     |                |

| Abstraction in Software Model Checking: Principles and Practice                                                              | 14             |

| Software Model Checking                                                                                                      |                |

| Symmetry Reduction Criteria for Software Model Checking                                                                      | 22             |

| Bytecode Model Checking: An Experimental Analysis                                                                            | 42             |

| The Influence of Software Module Systems on Modular Verification 6  Harry C. Li, Kathi Fisler, and Shriram Krishnamurthi     | 60             |

| Extending the Translation from SDL to Promela                                                                                | 79             |

| Algorithms and Theoretical Foundations                                                                                       |                |

| Model Checking Knowledge and Time                                                                                            | <del>)</del> 5 |

| Partial Order Reduction in Directed Model Checking                                                                           | 12             |

| Local Parallel Model Checking for the Alternation-Free $\mu$ -Calculus 12 Benedikt Bollig, Martin Leucker, and Michael Weber | 28             |

| Applications                                                                                                                 |                |

| The Agreement Problem Protocol Verification Environment                                                                      | 18             |

# SAT-Based Counterexample Guided Abstraction Refinement

Edmund M. Clarke

Department of Computer Science Carnegie Mellon University

(This is joint research with Anubhav Gupta and Ofer Strichman)

Abstract. We describe new techniques for model checking in the counterexample guided abstraction / refinement framework. The abstraction phase 'hides' the logic of various variables, hence considering them as inputs. This type of abstraction may lead to 'spurious' counterexamples, i.e. traces that cannot be simulated on the original (concrete) machine. We check whether a counterexample is real or spurious with a SAT Checker. We then use a combination of Integer Linear Programming (ILP) and machine learning techniques for refining the abstraction based on the counterexample. The process is repeated until either a real counterexample is found or the property is verified. We have implemented these techniques on top of the model checker NuSMV and the SAT solver Chaff. Experimental results prove the viability of these new techniques.

# Abstract Interpretation: Theory and Practice

Patrick Cousot

École normale supérieure

Département d'informatique

45 rue d'Ulm

75230 Paris cedex 05, France

Patrick.Cousot@ens.fr

http://www.di.ens.fr/~cousot/

Our objective in this talk is to give an intuitive account of abstract interpretation theory [1,2,3,4,5] and to present and discuss its main applications [6].

Abstract interpretation theory formalizes the conservative approximation of the semantics of hardware or software computer systems. The *semantics* provides a formal model describing all possible behaviors of a computer system in interaction with any possible environment. By *approximation* we mean the observation of the semantics at some level of abstraction, ignoring irrelevant details. *Conservative* means that the approximation can never lead to an erroneous conclusion.

Abstract interpretation theory provides thinking tools since the idea of abstraction by conservative approximation is central to reasoning (in particular on computer systems) and mechanical tools since the idea of an effectively computable approximation leads to a systematic and constructive formal design methodology of automatic semantics-based program manipulation algorithms and tools (e.g. [7]).

**Semantics** have been studied in the framework of abstract interpretation [8,9] and compared according to their relative precision. A number of semantics including among others small-step, big-step, termination and nontermination semantics, Plotkin's natural, Smyth's demoniac, Hoare's angelic relational and corresponding denotational semantics, Dijkstra's weakest precondition and weakest liberal precondition predicate transformers and Hoare's partial and total axiomatic semantics have all been derived by successive abstractions starting from an operational maximal trace semantics of a transition system. This results in a hierarchy of semantics providing a complete account of the structure and relative precision of most well-known semantics of programming languages [10].

**Program transformation** (such as online and offline partial evaluation, program monitoring (e.g. for security policy enforcement or scheduling), etc.) is an abstract interpretation [11] where the program syntactic transformation is an effective approximation of a corresponding undecidable transformation of the program semantics. The correctness of this program transformation is expressed as an observational equivalence of the subject and transformed semantics at some level of abstraction.

**Typing**, that is formal type systems and type inference algorithms, is an approximation of the denotational semantics of higher-order functional programs

D. Bošnački and S. Leue (Eds.): SPIN 2002, LNCS 2318, pp. 2-5, 2002.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2002

[12]. The abstraction is powerful enough to show statically that "typable programs cannot go wrong" in that the denotational semantics of these programs cannot raise at run-time those errors excluded by typing. This point of view leads to a hierarchy of type systems, which is part of the lattice of abstract interpretations of the untyped lambda-calculus. This hierarchy includes classical Milner/Mycroft and Damas/Milner polymorphic type schemes, Church/Curry monotypes and Hindley principal typing algorithm as well as new à la Church/Curry polytype systems.

Model-checking classical linear-time and branching-time state-based algorithms are sound and complete abstract interpretations of the trace-based semantics of transition systems [13]. Surprisingly, for the  $\hat{\mu}$ -calculus, a novel general temporal specification language featuring a natural and rich time-symmetric trace-based semantics, model-checking turned out to be incomplete, even for finite systems [13]. Moreover, any model-checking algorithm for the  $\hat{\mu}$ -calculus abstracting away from sets of traces will be necessarily incomplete [14].

Static program analysis is the first and most prevalent application of abstract interpretation [1,3,4]. By effective approximation of the fixpoint semantics of programs through abstraction [3,4] and convergence acceleration [3,15], a program analyzer will produce maybe incomplete but always sound information about the run-time behavior of programs. Abstract interpretation provides a general theory behind all program analyzers, which only differ in their choice of considered programming languages (e.g. imperative [16,17], parallel [18,19], functional [20], logic [21], etc), program properties (among many others, runtime errors [16,22], precision [23], security [24,25], fair liveness [26], probabilistic termination [27], etc) and their abstractions. Finally, we will discuss the various possible designs of program analyzers, from general-purpose to application-specific ones.

#### References

- Cousot, P.: Méthodes itératives de construction et d'approximation de points fixes d'opérateurs monotones sur un treillis, analyse sémantique de programmes. Thèse d'État ès sciences mathématiques, Université scientifique et médicale de Grenoble, Grenoble (1978)

- Cousot, P.: Semantic foundations of program analysis. In Muchnick, S., Jones, N., eds.: Program Flow Analysis: Theory and Applications. Prentice-Hall (1981) 303–342

- Cousot, P., Cousot, R.: Abstract interpretation: a unified lattice model for static analysis of programs by construction or approximation of fixpoints. In: 4<sup>th</sup> POPL, Los Angeles, ACM Press (1977) 238–252

- Cousot, P., Cousot, R.: Systematic design of program analysis frameworks. In: 6<sup>th</sup> POPL, San Antonio, ACM Press (1979) 269–282

- Cousot, P., Cousot, R.: Abstract interpretation frameworks. J. Logic and Comp. 2 (1992) 511–547

- Cousot, P.: Abstract interpretation based formal methods and future challenges, invited paper. In Wilhelm, R., ed.: « Informatics — 10 Years Back, 10 Years Ahead ». Volume 2000 of LNCS. Springer-Verlag (2000) 138–156

- Cousot, P.: Calculational design of semantics and static analyzers by abstract interpretation. NATO Int. Summer School 1998 on Calculational System Design. Marktoberdorf. Organized by F.L. Bauer, M. Broy, E.W. Dijkstra, D. Gries and C.A.R. Hoare. (1998)

- 8. Cousot, P.: Constructive design of a hierarchy of semantics of a transition system by abstract interpretation. ENTCS 6 (1997) http://www.elsevier.nl/locate/entcs/volume6.html, 25 pages.

- 9. Cousot, P., Cousot, R.: Inductive definitions, semantics and abstract interpretation. In: 19<sup>th</sup> POPL, Albuquerque, ACM Press (1992) 83–94

- 10. Cousot, P.: Constructive design of a hierarchy of semantics of a transition system by abstract interpretation. Theoret. Comput. Sci. (To appear (Preliminary version in [8]))

- Cousot, P., Cousot, R.: Systematic design of program transformation frameworks by abstract interpretation. In: 29<sup>th</sup> POPL, Portland, ACM Press (2002) 178–190

- 12. Cousot, P.: Types as abstract interpretations, invited paper. In:  $24^{th}$  POPL, Paris, ACM Press (1997) 316–331

- Cousot, P., Cousot, R.: Temporal abstract interpretation. In: 27<sup>th</sup> POPL, Boston, ACM Press (2000) 12–25

- Ranzato, F.: On the completeness of model checking. In Sands, D., ed.: Proc. 10<sup>th</sup>

ESOP '2001. Genova, 2–6 Apr. 2001, LNCS 2028, Springer-Verlag (2001) 137–154

- Cousot, P., Cousot, R.: Comparing the Galois connection and widening/narrowing approaches to abstract interpretation, invited paper. In Bruynooghe, M., Wirsing, M., eds.: Proc. 4<sup>th</sup> Int. Symp. PLILP '92. Leuven, 26–28 Aug. 1992, LNCS 631, Springer-Verlag (1992) 269–295

- 16. Cousot, P., Cousot, R.: Static determination of dynamic properties of programs. In: Proc.  $2^{nd}$  Int. Symp. on Programming, Dunod (1976) 106–130

- Cousot, P., Cousot, R.: Static determination of dynamic properties of recursive procedures. In Neuhold, E., ed.: IFIP Conf. on Formal Description of Programming Concepts, St-Andrews, Canada, North-Holland (1977) 237–277

- Cousot, P., Cousot, R.: Semantic analysis of communicating sequential processes. In de Bakker, J., van Leeuwen, J., eds.: 7<sup>th</sup> ICALP. LNCS 85, Springer-Verlag (1980) 119–133

- 19. Cousot, P., Cousot, R.: Invariance proof methods and analysis techniques for parallel programs. In Biermann, A., Guiho, G., Kodratoff, Y., eds.: Automatic Program Construction Techniques. Macmillan (1984) 243–271

- Cousot, P., Cousot, R.: Higher-order abstract interpretation (and application to comportment analysis generalizing strictness, termination, projection and PER analysis of functional languages), invited paper. In: Proc. 1994 ICCL, Toulouse, IEEE Comp. Soc. Press (1994) 95–112

- 21. Cousot, P., Cousot, R.: Abstract interpretation and application to logic programs. J. Logic Programming 13 (1992) 103–179 (The editor of J. Logic Programming has mistakenly published the unreadable galley proof. For a correct version of this paper, see http://www.di.ens.fr/~cousot.).

- Miné, A.: A new numerical abstract domain based on difference-bound matrices. In Danvy, Filinski, A., eds.: Proc. 2<sup>nd</sup> Symp. PADO '2001. Århus, 21–23 May 2001, LNCS 2053, Springer-Verlag (2001) 155–172

- 23. Goubault, É.rtel, M., Putot, S.: Asserting the precision of floating-point computations: a simple abstract interpreter. In: Proc. 11<sup>th</sup> ESOP '02. Grenoble, Springer-Verlag (2002)

- Blanchet, B.: An efficient cryptographic protocol verifier based on prolog rules.

In: 14<sup>th</sup> IEEE Computer Security Foundations Workshop (CSFW-14)pe Breton,

Canada, IEEE Comp. Soc. Press (2001) 82–96

- Feret, J.: Abstract interpretation-based static analysis of mobile ambients. In Cousot, P., ed.: Proc. 8<sup>th</sup> Int. Symp. SAS '01. Paris, LNCS 2126, Springer-Verlag (2001) 413–431

- 26. Mauborgne, L.: Tree schemata and fair termination. In Palsberg, J., ed.: Proc.  $7^{th}$  Int. Symp. SAS '2000. Santa Barbara, LNCS 1824. Springer-Verlag (29 June 1 Jul. 2000) 302–321

- 27. Monniaux, D.: An abstract analysis of the probabilistic termination of programs. In Cousot, P., ed.: Proc. 8<sup>th</sup> Int. Symp. SAS '01. Paris, LNCS 2126, Springer-Verlag (2001) 111–127

# SPIN Tutorial: How to Become a SPIN Doctor

(Extended Abstract)

Theo C. Ruys

Faculty of Computer Science, University of Twente, P.O. Box 217, 7500 AE Enschede, The Netherlands http://www.cs.utwente.nl/~ruys/

**Abstract.** SPIN is a model checker for the verification of software systems. SPIN uses a high level language called PROMELA to specify systems descriptions. The goal of this tutorial is to introduce novice users to both PROMELA and SPIN. The tutorial itself is divided into two parts. The BASIC SPIN part is targeted towards novice users of SPIN. The ADVANCED SPIN part of the tutorial could also be of considerable interest to intermediate SPIN users.

#### 1 Introduction

SPIN [2,3] is a model checker for the verification of software systems. During the last decade, SPIN has been successfully applied to trace logical design errors in distributed systems, such as operating systems, data communications protocols, switching systems, concurrent algorithms, railway signaling protocols, etc. [7]. SPIN checks the logical consistency of a specification; it reports on deadlocks, unspecified receptions, flags incompleteness, race conditions, and unwarranted assumptions about the relative speeds of processes [2]. SPIN is considered to be one of the most powerful and advanced model checkers (freely) available today. SPIN is widely distributed and has a large user base.

SPIN Beginner's Tutorial. SPIN uses a high level language called PROMELA (PROcess MEta LAnguage) to specify systems descriptions. The purpose of this tutorial at the SPIN 2002 Workshop is to introduce novice users to both PROMELA and SPIN. The first part of the tutorial (BASIC SPIN) gives an introduction to PROMELA and presents an overview of the validation and verification features of SPIN. The material will be illustrated by several demo's using XSPIN, the graphical user interface to SPIN. The second part of the tutorial (ADVANCED SPIN) discusses guidelines to construct efficient PROMELA models and shows how to use SPIN in the most effective way. Topics to be discussed include: SPIN's optimisation algorithms, directives and options to tune verification runs with SPIN, guidelines for effective PROMELA modelling, using SPIN as a debugger, validation management, etc.

D. Bošnački and S. Leue (Eds.): SPIN 2002, LNCS 2318, pp. 6–13, 2002.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2002

Although the "Spin Beginner's Tutorial" at the Spin 2002 Workshop will be targeted towards novice users of Spin, this 'extended abstract' focuses more on some advanced Spin topics. The reason for not including 'beginner's material' is twofold. First of all, an abstract is clearly too short to present a thorough introduction to Spin and Promela. But more importantly, there is already a wealth of excellent introductory material available on Spin; either online or in print (see below).

The organisation of this extended abstract is as follows. To guide the beginning Spin user through all the available Spin material, Section 2 provides some pointers to Spin resources. Section 2 also presents a general procedure that can be followed when verifying a property with Xspin. Section 3 presents several guidelines with respect to the effective use of Promela and Spin. Some of these guidelines may be too concise to be fully understood. Most of the topics in this extended abstract, however, are discussed in much greater depth in the author's PhD Thesis [10].

#### 2 Basic SPIN

SPIN Material. As said, this paper is not meant as a tutorial for PROMELA or SPIN. Users not yet familiar with the basic operations of SPIN have to turn to other sources of introductory information on SPIN. The usual first piece of advice for beginning users is as always: RTFM – Read The Fine Manual. And this time, the documentation is really fine. Apart from the book on the first version of SPIN by Gerard Holzmann [3], the recent versions of SPIN come with extensive online documentation in accessible .html format on both the tool and the PROMELA language. For beginning users of SPIN, the following documents are highly recommended:

- (online) The Basic Spin Manual [11] is a general introduction to the language Promela and the tool Spin. This document only discusses the basic use of Spin. It does not discuss extensions to the language that have been introduced in the later versions of Spin, i.e. 2.x and 3.x, which are documented elsewhere [15].

- (online) The document Guidelines for Verification with XSPIN [12] explains how to use SPIN using the graphical interface XSPIN, which runs independently from SPIN itself and helps by generating the proper SPIN commands based on menu selections.

- And albeit slightly older, [4] is still a good tutorial to get started with SPIN. Naturally, the newer language and tool additions are not covered, but the core of the system which has not changed over the years is nicely introduced.

After browsing these documents, one is advised to plunge into the comprehensive set of examples and exercises:

■ SPIN Verification Examples and Exercises – a sample set of exercises with SPIN [13].

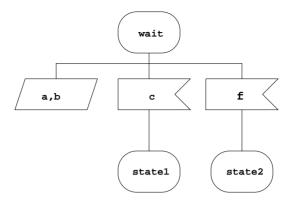

General procedure to verify a (general) property  $\phi$  on a Promela model M using the model checker Spin:

- 1. Sanity check. Perform some interactive and random simulation runs on the model M and the property  $\phi$  either using XSPIN or SPIN.

- 2. Partial check. Use Spin's bitstate hashing mode to quickly sweep over the state space. Spin's bitstate hashing mode is fast and if there are some silly mistakes in the model, chances are high, that Spin will find them quickly. This 'partial check' is especially useful if the model M is big and it is estimated that the verification will take considerable time.

- 3. Exhaustive check. Run an exhaustive check on the model M and the property  $\phi$ . If the exhaustive verification fails because there is not enough memory to hold the complete state space, there are several ways to proceed:

- Compression. Try one of SPIN's memory compression options, to reduce the size of the state space.

- The compile-time option -DCOLLAPSE collapses state vectors sizes by up to 80% to 90% [6].

- The compile-time option -DMA=N makes pan use a minimized DFA encoding [8] for the state space assuming a maximum of N bytes in the state vector. This option is very effective, but will also increase the running time of the verification run considerably.

Both options can be combined.

- Optimisations. Make sure that the model is optimised in terms of the number of states and the size of the state vector. Follow the guidelines in Section 3 to optimise the model M as aggressively as possible.

- Abstractions. If the memory compression options do not work (or are not really an option due the implications on the time of the verification run), one should try to make the model M smaller by making abstractions of the model. Go back to step 1 and try to verify the abstracted model.

- Bitstate hashing: If the other methods do not work to get M verified, one might use Spin's bitstate hashing or hash compaction verification modes to partially verify the model.

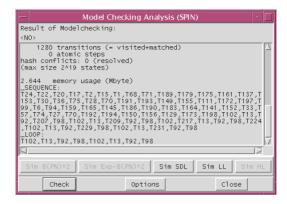

Fig. 1. Verification of a property  $\phi$  for a Promela model M using the model checker Spin.

The investment into the exercises will be well spent in the sense that one will get a good feeling of the systems and Promela models that can be analysed with Spin.

For the intermediate to advanced user, the online documentation contains reference information on all language constructs [14] and a concise language reference by Rob Gerth [1]. The SPIN community is quite active in testimony whereof the (at least) yearly SPIN Workshops, which are being organised since 1995. The proceedings of these workshops – which are publicly available online via the SPIN home-page [2] – contain a wealth of information on, among others:

- discussions on new and significant algorithms within Spin;

- contributions and proposals to improve or extend Spin;

- reports on (successful) industrial applications with Spin;

- proven best practices when applying Spin.

Validation Procedure. XSPIN is a so-called *Integrated Validation Environment* (IVE) on top of SPIN; it allows the user to edit, simulate and verify PROMELA models. Most users start using SPIN through XSPIN. For casual use and small to moderate verification projects, XSPIN suffices. And even for the more advanced user of SPIN, XSPIN is very convenient as it releases the user of remembering all options and directives to tune the verification runs with SPIN: most of these options can be set via dialog boxes within XSPIN.

Although XSPIN is user-friendly and straightforward to use, most beginning SPIN users do not know where to start to effectively apply XSPIN (or SPIN) to check a property. Fig. 1 presents a validation procedure to verify a model M against a property  $\phi$  using XSPIN. Step 1. and 2. of Fig. 1 require some user guidance and inspection but are generally quite fast. Step 3. may take much longer but after pressing the Run button does not need any additional user input.

#### 3 Advanced SPIN

In this section we discuss some more advanced topics with respect to application of Spin. We focus on the effective use of the modelling language Promela. In the tutorial at the Spin 2002 Workshop other more pragmatic issues will be discussed as well.

Extreme Modelling. Now that model checking tools in general and SPIN in particular are becoming more widespread in use [5], these tools are starting to be applied by people that only want to press the button and that do not know precisely what is 'under the hood' of such verification tools. Press-the-button verification is only feasible for small to medium-sized applications. Industrialsize applications need aggressive use of the modelling language, the properties to be checked and the verification tool itself. There is generally a big difference in efficiency in the models developed by a 'casual' user and the models developed by an 'expert' user. Moreover, the 'expert' user knows how to exploit the directives and options of the model checker to optimise the verification runs. Efficient use of model checking tools seems to require an 'assembler programming' approach to model building: use all tricks of the model checker to minimise the state space of the model and make the verification process as efficient as possible. The 'expert' verification engineer resembles the seasoned programmer, who not only has a deep knowledge and understanding of data structures and algorithms but also knows the options and directives to tune the programming tools that he or she is using.

From XSPIN's Help, Reducing Complexity dialog box:

When a verification cannot be completed because of computational complexity; here are some strategies that can be applied to combat this problem.

- 0. Slicing. Run the Slicing Algorithm (in the Run Menu) to find potential redundancy in your model for the stated properties.

- 1. Abstraction. Try to make the model more general, more abstract. Remember that you are constructing a verification model and not an implementation. SPIN's strength is in proving properties of interactions in a distributed system (the implicit assumptions that processes make about each other) its strength is not in proving things about local computations, data dependencies, etc.

- 2. Redundancy. Remove everything that is not directly related to the property you are trying to prove: redundant computations, redundant data. Avoid counters; avoid incrementing variables that are used for only book-keeping purposes. The Syntax Check in the Run Menu option will warn about the gravest offenses.

- 3. Channels. Asynchronous channels are a significant source of complexity in verification. Use a synchronous (rendez-vous) channel where possible. Reduce the number of slots in asynchronous channels to a minimum (use 2, or 3 slots to get started).

- 4. Intermediate processes. Look for processes that merely transfer messages. Consider if you can remove processes that only copy incoming messages from one channel into another, by letting the sender generate the final message right away. If the intermediate process makes choices (e.g. to delete or duplicate, etc.), let the sender make that choice, rather than the intermediate process.

- Local computations. Combine local computations into atomic or d\_step sequences.

- 6. Temporary data. Avoid leaving scratch data around in variables. You can reduce the number of states by, for instance, resetting local variables that are used inside atomic sequences to zero at the end of those sequences; so that the scratch values aren't visible outside the sequence. Alternatively: introduce some extra global 'hidden' variables for these purposes (see the WhatsNew.html document [15]). Use the predefined variable "\_" as a write-only scratch variable wherever possible.

- 7. Combine behaviour. If possible to do so: combine the behaviour of two processes into a single one. Generalise behaviour; focus on coordination aspects (i.e. the interfaces between processes), rather than the local computation inside processes.

- 8. Exploit PO. Try to exploit the partial order reduction strategies. Use the xr and xs assertions (see WhatsNew.html [15]); avoid sharing channels between multiple receivers or multiple senders. Avoid merging independent data-streams into a single shared channel.

Fig. 2. The Reducing Complexity guidelines of the XSPIN 3.4.x Help.

Guidelines to construct Promela models for efficient verification with Spin:

- The macro processor m4 is more powerful than cpp and can be used to generalise PROMELA models.

- Beware of infinite loops in the presence of atomic and d\_step clauses.

- A non-deterministic random construct should be constructed using an ifclause.

- Do not use an array of bits in Promela; use a (self-defined) bitvector instead.

- Variables whose values are always smaller than 16 should be declared as unsigned variables.

- User defined types can be efficiently implemented in PROMELA using (inline) macros and d\_step constructs.

- Lossy channels can best be modelled by letting the sending process 'lose' messages or by a 'stealing daemon' process.

- A multicast or broadcast application is best modelled on top of a multicast or broadcast service.

- Use *local* variables for variables that are only used within a single process. If a local variable is to be used in a never claim, one should define it as a local *global* variable.

- PROMELA processes that may terminate should not be created last in a PROMELA model, unless you want the terminating processes to be replaced by new processes.

- Do not use an unguarded monitor process with an assert statement to check for invariance if the original model contains a timeout statement.

- Changing the layout of the state vector can have (positive) effects on the effectiveness of Spin's bitstate hashing mode.

- When checking an invariant property with Spin, use a monitor process with a guarded assert statement.

Fig. 3. Summary of the PROMELA and SPIN 'recipes' presented in [9,10].

Fortunately, it is not necessary to become an 'expert' verification engineer to use Spin *effectively*. Several pragmatic guidelines and rules of thumb have been identified over the last few years which can be applied by novice and intermediate users to develop verification-effective Promela models (see below).

**Optimisation Order.** With model checking tools there is – just as with programming – a trade-off between time and space requirements. For the model checking process, however, the space requirements are much more important than the time requirements. With respect to effective model checking with SPIN, the following optimisation order should be adopted:

1. Number of states. Because of the state space explosion, it is crucial to reduce the number of states as much as possible. So reduction of the number of states is the first consideration.

- 2. State vector size. The minimization of the size of the state vector (i.e. the amount of memory which is needed to encode a single state) is the next concern.

- 3. Size of search stack. Our next priority lies with the minimisation of SPIN's depth-first search stack of states.

- 4. Verification time. Only in the last case, reduction of the verification time should be taken into account.

SPIN has several optimisation algorithms to make verification runs more effective, for instance: partial order reduction, minimised automaton encoding of states, state vector compression and bitstate hashing. SPIN supports several command-line options and directives to tune these optimisation algorithms. Not surprisingly, many of these options are related to the trade-off between space and time requirements. Within XSPIN, these options and directives can be accessed and modified via: Run  $\rightarrow$  Set Verification Parameters  $\rightarrow$  Set Advanced Options. These options and directives are concisely explained in XSPIN's Help.

**Reducing Complexity.** In Fig. 1 we mentioned that one should *optimise* the PROMELA model to make the verification with SPIN feasible. Users that are new to SPIN, however, might not know what is meant by an 'optimised' PROMELA model.

The best advice to reduce the complexity of a PROMELA model stems from the help system of the XSPIN program itself. Under Help, Reducing Complexity, Gerard Holzmann has listed several rules of thumb that should be applied first to reduce the complexity of the PROMELA model under verification. For reference, we have included this list of guidelines in Fig. 2. The SPIN user who already lives by all these rules-of-thumb, is on the right track.

Additional Guidelines. For his PhD Thesis [10], the author has investigated several 'expert' techniques to optimise both the modelling and verification process when using Spin. These techniques are mostly concerned with the minimisation of the number of states or the reduction of the state vector. The proposed techniques are verified and checked using numerous controlled experiments with Spin itself. Fig. 3 summarises most lessons learned from [9,10]. In the tutorial at the Spin 2002 Workshop a few of these guidelines will be discussed in greater depth.

#### 4 Conclusions

SPIN is considered to be one of the most powerful and advanced model checkers (freely) available today. When provided with a model M and a property  $\phi$  to be verified, in principle, SPIN comes up with a result fully automatically. Problems arise when the state space of the PROMELA model is too large to be checked exhaustively. Although users of SPIN do not have to know what is happening 'under-the-hood' of SPIN, one should obey certain 'rules-of-thumb' to reduce the complexity of PROMELA models as much as possible. SPIN users should be aware of these guidelines when constructing their verification models.

#### Acknowledgements

Gerard Holzmann, the Spin master, is thanked for his approval to reprint the Reducing Complexity guidelines of Xspin in this paper.

#### References

- 1. R. Gerth. Concise Promela Reference. Accessible from [2].

- 2. G. J. Holzmann. Spin homepage: http://netlib.bell-labs.com/netlib/spin/.

- G. J. Holzmann. Design and Validation of Computer Protocols. Prentice Hall, Englewood Cliffs, New Jersey, USA, 1991.

- G. J. Holzmann. Tutorial: Design and Validation of Protocols. Computer Networks and ISDN Systems, 25(9):981–1017, 1993.

- G. J. Holzmann. Spin Model Checking Reliable Design of Concurrent Software. Dr. Dobb's Journal, pages 92–97, October 1997.

- G. J. Holzmann. State Compression in Spin: Recursive Indexing and Compression Training Runs. In *Proceedings of SPIN97*, the Third International Workshop on SPIN, University of Twente, Enschede, The Netherlands, April 1997. Also available from URL: http://netlib.bell-labs.com/netlib/spin/ws97/gerard.ps.Z.

- G. J. Holzmann. The Model Checker Spin. IEEE Transactions on Software Engineering, 23(5):279–295, May 1997.

- G. J. Holzmann and A. Puri. A Minimized Automaton Representation of Reachable States. Software Tools for Technology Transfer (STTT), 3(1), 1999.

- T. C. Ruys. Low-Fat Recipes for SPIN. In K. Havelund, J. Penix, and W. Visser, editors, SPIN Model Checking and Software Verification, Proceedings of the 7th International SPIN Workshop (SPIN'2000), volume 1885, pages 287–321, Stanford, California, USA, August 2000.

- T. C. Ruys. Towards Effective Model Checking. PhD thesis, University of Twente, Enschede, The Netherlands, March 2001. Available from the author's homepage.

- 11. Spin Online Documentation. Basic Spin Manual. Accessible from [2].

- 12. Spin Online Documentation. Guidelines for Verification with XSPIN Spin Verifier's Roadmap: using XSPIN. Accessible from [2].

- 13. Spin Online Documentation. Spin Verification Examples and Exercises. Accessible from [2].

- 14. Spin Online Documentation. Spin Version 3.3: Language Reference Man-Pages and Semantics Definition. Accessible from [2].

- 15. Spin Online Documentation. What's New in Spin Versions 2.0 and 3.0 Summary of changes since Version 1.0. Accessible from [2].

# **Abstraction in Software Model Checking: Principles and Practice**

(Tutorial Overview and Bibliography)

#### **Dennis Dams**

Bell Labs, Lucent Technologies, 600 Mountain Ave, Murray Hill, NJ 07974, USA dennis@research.bell-labs.com

**Abstract.** This paper provides a brief description, including a bibliography, of the SPIN2002 tutorial on abstraction in model checking of software.

#### 1 Introduction

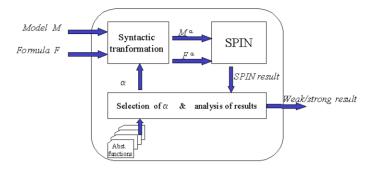

The tutorial assumes familiarity with the principles of model checking ( [CGP99]), which is an approach to the formal verification of temporal correctness properties of finite state systems. The starting point of a model checker is a verification model: a formal system description, called *abstract system* henceforth, having a state space that is small enough to render model checking feasible. The goal is to establish correctness of the original system being modelled. When a (more detailed) formal description is also available for this *concrete system*, one can try and formalize the relation between these systems, possibly with the aim of offering automated support for the abstraction process. In the context of model checking, the term *abstraction* refers to methodology, theory, techniques, and tools that deal with the relation between formalized system descriptions at different levels of detail.

Abstraction methodologies are concerned with the process of abstraction: Given a concrete system and a property to be checked, how to get to a suitable abstract system? This process typically involves a form of trial-and-error, and depends on rules-of-thumb and ingenuity. Abstraction theory focuses on formalizing the relation between the semantic models of concrete and abstract systems. A prime requirement of such a relation is that it ensures *preservation* of correctness properties: A property checked to be true for the abstract system should also hold for the concrete system being modelled. By abstraction techniques we mean the methods that can be employed to construct abstract systems from concrete ones. These range from slicing and variable hiding to more general, less algorithmic approaches like program transformation based on abstract interpretation, which may require human interaction. There exist several software tools that implement such abstraction techniques. At its front end such a tool offers what is essentially a programming language in which a system description may be entered. The core of the tool consists of a collection of components that implement techniques, sometimes several alternative ones, for abstraction. Also, methodological guidelines may be provided aiding in the selection of a sequence of abstraction steps. At the back end, a verification model is then produced in a form that is accepted by a model checker.

As abstraction is a very broad field, we cannot discuss all relevant approaches. Techniques that can be viewed as instances of abstraction but that will not be further touched upon here include data-independence, (de)compositionality, parameterization, partial order reduction, real time verification, and symmetry techniques. The focus will be mostly on model checking of software source code – as a consequence BBD-based approaches to abstraction will receive less attention.

Much of the tutorial is based on [Dam96].

#### 2 Methodology

There is relatively little research into the methodological aspects of combining model checking and abstraction. Generally, the process follows the cycle that occurs in all approaches to software validation. For the case of model checking the steps are summarized in [CGP99], p. 4: modeling, specification, verification. If the last of these steps fails, then inspection of the counterexample will indicate an error in the system, in the model, or in the specification, leading to a repetition of the steps.

For an approach that combines model checking with formal abstraction, an instance of this cycle is commonly proposed. In this setting, the model can be viewed as the result of applying an abstraction to the concrete system, and thus the triple (system, model, specification) may be replaced by (system, abstraction, specification). A negative answer produced by running a model checker on this may indicate an error in any of the three ingredients. The term *false negative* refers to the case that the abstraction is too coarse – inspection of the counterexample may then suggest a way to refine it.

More or less explicit descriptions of methodologies are found in [BH99, BR01, DHJ<sup>+</sup>01, Hol01, HS02, LBBO01, WC99], often embedded in reports on case studies, or in descriptions of verification tools by which they are supported. A paper discussing methodological issues in formal methods at a more general level is [Hei98].

# 3 Theory

Because of its strong roots in the formal methods community, there is a large body of theory on abstraction. Here we focus on papers that provide the common theoretical underpinnings. Papers that provide the foundations for specific techniques and tools may be found through references given in the sections below.

State-transition systems are commonly used as the formal semantics on both the concrete and abstract sides. Results on property-preserving relations between these draw on the theory of formal languages and automata ( [HU79]), in particular on results about homomorphisms and language inclusion ( [Gin68]), minimization and partition refinement ( [BFH+92, GV90, Hop71, KS90, PT87]), and on extensions of automata to infinite words ( [Buc60]). The topic of comparative semantics has also been extensively studied in the context of process algebra ( [BW90]), see e.g. [DN87, vG90]. In particular the notion of bisimulation ( [Par81]), weaker equivalences and pre-orders related to it ( [GW89,Mil71,Mil80]), and their connection to modal and temporal logic ( [ASB+94, BCG88,BFG+91,BR83,Cho95,DNV90,GKP92,GS84,HM80,Kur94,Sti89,vBvES94]) are relevant.

The partition refinement algorithms mentioned above may be used in a *quotient construction* that produces a minimal transition system that is equivalent to the original system under some notion of behavioural (bisimulation-like) equivalence. The starting point for model checking under abstraction is usually a more drastically reduced system which is related to the concrete system through a behavioural pre-order like simulation ([CGL94]). The satisfaction of (temporal) logic formulas over these abstract systems is usually non-standard: properties may evaluate to "unknown" as a result of abstracting away certain information. A similar notion of incomplete information is common in the related area of program analysis and Abstract Interpretation ([CC77, NNH99]). Reasoning with it in terms of modal and temporal logic, in the context of model checking, is a topic that is receiving considerable attention: [BG99, CDE+01, DGG00a, HJS01]. An overview of many-valued modal logics is given in [Fit91, Fit92].

In a general framework for abstracting transition systems that accommodates for the preservation of universal as well as existential temporal properties, not only the evaluation of atomic propositions in states, but also the treatment of transitions between states becomes non-standard. Notions of abstract transition systems that feature two different, dual transition relations are presented in [CIY94, DGG94, GHJ01, Kel95], and the approach in [LGS<sup>+</sup>95] uses two separate transition systems – intuitively, one representing an over- and the other an under-approximation. *Modal transition systems* ( [LT88]) also combine two transition relations ("may" and "must") but there they are not strictly dual.

An orthogonal duality is formed by the distinction between *invariance* and *progress* properties. Although both are preserved in most of the frameworks mentioned above, abstraction tends to introduce more false counterexamples to progress than to safety properties. In terms of Floyd-Hoare style correctness proofs, abstractions tend to be more like *invariants* than *ranking functions*. This problem is addressed in [BLS00, CS01, DGG00b].

The question whether a finite abstraction that is suitable for model checking any given temporal property always exists, is answered positively in [KPV99].

# 4 Techniques/Algorithms

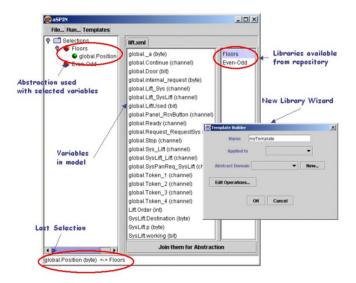

Abstraction techniques are the methods or algorithms that can be employed to construct abstract systems from concrete ones. One approach consist in having the user choose *abstract interpretations*, given a concrete system and a property to be verified. These are replacements of data types with smaller-sized types that only reflect certain aspects of the original values; operations on these types will then have to be lifted correspondingly. Such abstracted data types may already exists, e.g. in the form of a library, or they may be newly constructed ( [DHJ+01, dMGM99]). In the latter case, *safety* of the abstractions may have to be proven ( [SBLS99]).

More ambitious are the attempts to automatically derive suitable abstractions, e.g. [ASSSV94, BLO98, CU98, DGG93, GS97, NK00, RS99]. The technique proposed in [GS97] is now known as *predicate abstraction* and has inspired many case studies, tools, and approaches to abstraction refinement, see e.g. [AKN02, BHPV00, BMMR01, BPR, CGJ+00, DDP99, GQ01].

On the other hand there are several techniques that are less general but fully automatic, like slicing ( [HDZ00]), variable hiding ( [BH99, DHH02]), and localization reduction ( [Kur94]).

#### 5 Tools

Some tools that combine model checking with abstraction and the URLs at which they can be found are:

$\alpha$ **Spin**: http://polaris.lcc.uma.es/~gisum/fmse/tools/ **Bandera**: http://www.cis.ksu.edu/santos/bandera/

SLAM: http://www.research.microsoft.com/projects/slam/ FeaVer: http://cm.bell-labs.com/cm/cs/what/feaver/ InVeSt: http://www-verimag.imag.fr/~async/INVEST/

JPF: http://ase.arc.nasa.gov/visser/jpf/STeP: http://www-step.stanford.edu/

#### References

- AKN02. Nina Amla, Robert P. Kurshan, and Kedar S. Namjoshi. AutoAbs: Syntax-directed program abstraction, 2002. Submitted.

- ASB<sup>+</sup>94. Adnan Aziz, Vigyan Singhal, Felice Balarin, Robert K. Brayton, and Alberto L. Sangiovanni-Vincentelli. Equivalences for fair Kripke structures. In Serge Abiteboul and Eli Shamir, editors, *Automata, Languages and Programming*, number 820 in LNCS, pages 364–375, Springer-Verlag, Berlin, 1994.

- ASSSV94. Adnan Aziz, Thomas R. Shiple, Vigyan Singhal, and Alberto L. Sangiovanni-Vincentelli. Formula-dependent equivalence for compositional CTL model checking. In David L. Dill, editor, *Computer Aided Verification*, number 818 in LNCS, pages 324–337, Springer-Verlag, Berlin, 1994.

- BCG88. M.C. Browne, E.M. Clarke, and O. Grumberg. Characterizing finite Kripke structures in propositional temporal logic. *Journal of Theoretical Computer Science*, 59:115– 131, 1988.

- BFG<sup>+</sup>91. A. Bouajjani, J.C. Fernandez, S. Graf, C. Rodriguez, and J. Sifakis. Safety for branching time semantics. In J. Leach Albert, B. Monien, and M. Rodríguez Artalejo, editors, *Automata, Languages and Programming*, number 510 in LNCS, pages 76–92, Springer-Verlag, New York, 1991.

- BFH<sup>+</sup>92. A. Bouajjani, J.-C. Fernandez, N. Halbwachs, P. Raymond, and C. Ratel. Minimal state graph generation. *Science of Computer Programming*, 18:247–269, 1992.

- BG99. Glenn Bruns and Patrice Godefroid. Model checking partial state spaces with 3-valued temporal logics. In Halbwachs and Peled [HP99], pages 274–287.

- BH99. Ramesh Bharadwaj and Constance L. Heitmeyer. Model checking complete requirements specifications using abstraction. *Automated Software Engineering: An International Journal*, 6(1):37–68, January 1999.

- BHPV00. G. Brat, K. Havelund, S. Park, and W. Visser. Model checking programs. In *IEEE International Conference on Automated Software Engineering (ASE)*, 2000.

- BLO98. Saddek Bensalem, Yassine Lakhnech, and Sam Owre. Computing abstractions of infinite state systems compositionally and automatically. In Hu and Vardi [HV98], pages 319–331.

- BLS00. Kai Baukus, Yassine Lakhnech, and Karsten Stahl. Verifying universal properties of parameterized networks. In M. Joseph, editor, *Proceedings of the Sixth International Symposium on Formal Techniques in Real-Time and Fault-Tolerant Systems, FTRTFT2000*, number 1926 in LNCS, pages 291–303, Springer, Berlin, 2000.

- BMMR01. Thomas Ball, Rupak Majumdar, Todd Millstein, and Sriram K. Rajamani. Automatic predicate abstraction of C programs. *SIGPLAN Notices*, 36(5):203–213, 2001.

- BPR. Thomas Ball, Andreas Podelski, and Sriram K. Rajamani. Relative completeness of abstraction refinement for software model checking. To appear in TACAS 2002.

- BR83. Stephen D. Brookes and William C. Rounds. Behavioural equivalence relations induced by programming logics. In J. Diaz, editor, *Automata, Languages and Programming*, number 154 in LNCS, pages 97–108, Springer-Verlag, Berlin, 1983.

- BR01. Thomas Ball and Sriram K. Rajamani. Automatically validating temporal safety properties of interfaces. In Matthew Dwyer, editor, *Model Checking Software*, number 2057 in LNCS, pages 103–122, Springer, Berlin, 2001.

- Buc60. J. Buchi. Weak second-order arithmetic and finite automata. *Zeitschrift fur Mathematische Logik und Grundlagen der Mathematik*, 6:66–92, 1960.

- BW90. J.C.M. Baeten and W.P. Weijland. *Process Algebra*. Number 18 in Cambridge Tracts in Theoretical Computer Science. Cambridge University Press, Cambridge, 1990.

- CC77. P. Cousot and R. Cousot. Abstract interpretation: A unified lattice model for static analysis of programs by construction or approximation of fixpoints. In *Proc. 4th ACM Symp. on Principles of Programming Languages*, pages 238–252, Los Angeles, California, 1977.

- CDE<sup>+</sup>01. Marsha Chechik, Benet Devereux, Steve Easterbrook, Albert Y. C. Lai, and Victor Petrovykh. Efficient multiple-valued model-checking using lattice representations. In K. G. Larsen and M. Nielsen, editors, *International Conference on Concurrency Theory*, number 2154 in LNCS, pages 441–455, Springer, Berlin, 2001.

- CGJ<sup>+</sup>00. Edmund M. Clarke, Orna Grumberg, Somesh Jha, Yuan Lu, and Helmut Veith. Counterexample-guided abstraction refinement. In Emerson and Sistla [ES00], pages 154–169.

- CGL94. E.M. Clarke, O. Grumberg, and D.E. Long. Model checking and abstraction. *ACM Transactions on Programming Languages and Systems*, 16(5):1512–1542, September 1994.

- CGP99. Edmund M. Clarke, Orna Grumberg, and Doron A. Peled. *Model Checking*. The MIT Press, Cambridge, Mass., 1999.

- Cho95. Ching-Tsun Chou. A simple treatment of property preservation via simulation. Technical Report 950014, Comp. Sc. Dept., University of California at Los Angeles, March 1995.

- CIY94. R. Cleaveland, S. P. Iyer, and D. Yankelevich. Abstractions for preserving all CTL\* formulae. Technical Report 94-03, Dept. of Comp. Sc., North Carolina State University, Raleigh, NC 27695, April 1994.

- CS01. Michael Colon and Henny Sipma. Synthesis of linear ranking functions. In Margaria and Yi [MY01], pages 67–81.

- CU98. Michael Colon and Tomas E. Uribe. Generating finite-state abstractions of reactive systems using decision procedures. In Hu and Vardi [HV98], pages 293–304.

- Dam96. Dennis René Dams. Abstract Interpretation and Partition Refinement for Model Checking. PhD thesis, Eindhoven University of Technology, P.O. Box 513, 5600 MB Eindhoven, The Netherlands, July 1996.

- DDP99. Satyaki Das, David L. Dill, and Seungjoon Park. Experience with predicate abstraction. In Halbwachs and Peled [HP99], pages 160–171.

- DGG93. Dennis Dams, Rob Gerth, and Orna Grumberg. Generation of reduced models for checking fragments of CTL. In Costas Courcoubetis, editor, *Computer Aided Verification*, number 697 in LNCS, pages 479–490, Springer-Verlag, Berlin, 1993.

- DGG94. Dennis Dams, Orna Grumberg, and Rob Gerth. Abstract interpretation of reactive systems: Abstractions preserving ∀CTL\*, ∃CTL\* and CTL\*. In E.-R. Olderog, editor, *Proceedings of the IFIP WG2.1/WG2.2/WG2.3 Working Conference on Programming Concepts, Methods and Calculi (PROCOMET)*, IFIP Transactions, Amsterdam, June 1994. North-Holland/Elsevier.

- DGG00a. Dennis Dams, Rob Gerth, and Orna Grumberg. Fair model checking of abstractions (extended abstract). In Michael Leuschel, Andreas Podelski, C.R. Ramakrishnan, and Ulrich Ultes-Nitsche, editors, *Proceedings of the Workshop on Verification and Computational Logic (VCL'2000)*, number DSSE-TR-2000-6, University of Southampton, July 2000.

- DGG00b. Dennis Dams, Rob Gerth, and Orna Grumberg. A heuristic for the automatic generation of ranking functions. In Ganesh Gopalakrishnan, editor, *Workshop on Advances in Verification (WAVe'00)*, pages 1–8, School of Computing, university of Utah, July 2000.

- DGLM99. Dennis Dams, Rob Gerth, Stefan Leue, and Mieke Massink, editors. *Theoretical and Practical Aspects of SPIN Model Checking*, number 1680 in LNCS, Springer, Berlin, 1999.

- DHH02. Dennis Dams, William Hesse, and Gerard Holzmann. Abstracting C with abC, 2002. Submitted.

- DHJ<sup>+</sup>01. Matthew Dwyer, John Hatcliff, Roby Joehanes, Shawn Laubach, Corina Pasareanu, Robby, Willem Visser, and Hongjun Zheng. Tool-supported program abstraction for finite-state verification. In *Proceedings of the 23<sup>rd</sup> International Conference on Software Engineering*, Toronto, Canada, May 12-19 2001. ICSE 2001, IEEE Computer Society.

- dMGM99. Maria del Mar Gallardo and Pedro Merino. A framework for automatic construction of abstract promela models. In Dams et al. [DGLM99], pages 184–199.

- DN87. Rocco De Nicola. Extensional equivalences for transition systems. *Acta Informatica*, 24:211–237, 1987.

- DNV90. Rocco De Nicola and Frits Vaandrager. Three logics for branching bisimulation. In 1990 IEEE Fifth Annual Symposium on Logic in Computer Science, pages 118–129, Los Alamitos, CA, 1990. IEEE Computer Society Press.

- ES00. E. Allen Emerson and A. Prasad Sistla, editors. *Computer Aided Verification*, number 1855 in LNCS, Springer, Berlin, 2000.

- Fit91. Melvin Fitting. Many-valued modal logics. *Fundamenta Informaticae*, 15(3–4):335–3, 1991.

- Fit92. Melvin C. Fitting. Many-valued modal logics II. In A. Nerode and M. Taitslin, editors, *Proc. LFCS'92*, number 620 in LNCS. Springer-Verlag, 1992.

- GHJ01. Patrice Godefroid, Michael Huth, and Radha Jagadeesan. Abstraction-based model checking using modal transition systems. In K. G. Larsen and M. Nielsen, editors, *International Conference on Concurrency Theory*, number 2154 in LNCS, pages 426–440, Springer, Berlin, 2001.

- Gin68. A. Ginzburg. *Algebraic Theory of Automata*. ACM Monograph Series. Academic Press, New York/London, 1968.

- GKP92. Ursula Goltz, Ruurd Kuiper, and Wojciech Penczek. Propositional temporal logics and equivalences. In W.R. Cleaveland, editor, *CONCUR* '92, number 630 in LNCS, pages 222–236, Springer-Verlag, Berlin, 1992.

- GQ01. R. Giacobazzi and E. Quintarelli. Incompleteness, counterexamples and refinements in abstract model-checking. In P. Cousot, editor, *Proc. of The 8th International Static Analysis Symposium, SAS'01*, volume 2126 of *Lecture Notes in Computer Science*, pages 356–373. Springer-Verlag, 2001.

- GS84. S. Graf and J. Sifakis. A modal characterization of observational congruence on finite terms of CCS. In Jan Paredaens, editor, *Proc. of the Eleventh International Colloquium on Automata Languages and Programming (ICALP)*, number 172 in LNCS, pages 222–234, Springer-Verlag, Berlin, 1984.

- GS97. S. Graf and H. Saidi. Construction of abstract state graphs with PVS. In Orna Grumberg, editor, *Computer Aided Verification*, number 1254 in LNCS, pages 72–83, Springer, Berlin, 1997.

- GV90. Jan Friso Groote and Frits Vaandrager. An efficient algorithm for branching bisimulation and stuttering equivalence. In M. S. Paterson, editor, *Automata, Languages and Programming*, number 443 in LNCS, pages 626–638, Springer-Verlag, New York, 1990.

- GW89. R. J. van Glabbeek and W. P. Weijland. Branching time and abstraction in bisimulation semantics (extended abstract). In G. X. Ritter, editor, *Information Processing* 89, pages 613–618, Amsterdam, 1989. North-Holland.

- HDZ00. John Hatcliff, Matthew B. Dwyer, and Hongjun Zheng. Slicing software for model construction. *Higher-Order and Symbolic Computation*, 13(4):315–353, 2000.

- Hei98. Constance L. Heitmeyer. On the need for practical formal methods. In A.P. Ravn and H. Rischel, editors, *Formal Techniques in Real-Time and Fault-Tolerant Systems*, number 1486 in LNCS, pages 18–26, Springer, Berlin, 1998.

- HJS01. Michael Huth, Radha Jagadeesan, and David A. Schmidt. Modal transition systems: A foundation for three-valued program analysis. In D. Sands, editor, *Programming Languages and Systems*, number 2028 in LNCS, pages 155–169, Springer, Berlin, 2001.

- HM80. Matthew Hennessy and Robin Milner. On observing nondeterminism and concurrency. In J.W. de Bakker and J. van Leeuwen, editors, *Proc. of the Seventh International Colloquium on Automata Languages and Programming (ICALP)*, number 85 in LNCS, pages 299–309, Springer-Verlag, Berlin, 1980.

- Hol01. G.J. Holzmann. From code to models. In Proc. 2nd Int. Conf. on Applications of Concurrency to System Design, pages 3–10, Newcastle upon Tyne, U.K., June 2001.

- Hop71. John Hopcroft. An  $n \log n$  algorithm for minimizing states in a finite automaton. In Zvi Kohavi and Azaria Paz, editors, *Theory of Machines and Computations*, pages 189–196, Academic Press, New York, 1971.

- HP99. Nicolas Halbwachs and Doron Peled, editors. *Computer Aided Verification*, number 1633 in LNCS, Springer, Berlin, 1999.

- HS02. G.J. Holzmann and Margaret H. Smith. An automated verification method for distributed systems software based on model extraction. *IEEE Trans. on Software Engineering*, 28(4), April 2002.

- HU79. John E. Hopcroft and Jeffrey D. Ullman. *Introduction to Automata Theory, Languages, and Computation*. Addison-Wesley, Reading, Massachusetts, 1979.

- HV98. Alan J. Hu and Moshe Y. Vardi, editors. *Computer Aided Verification*, number 1427 in LNCS, Springer, Berlin, 1998.

- Kel95. Peter Kelb. Abstraktionstechniken für automatische Verifikationsmethoden. PhD thesis, Carl von Ossietzky University of Oldenburg, Germany, December 1995.

- KPV99. Y. Kesten, A. Pnueli, and M. Vardi. Verification by augmented abstraction: The automata-theoretic view. In *Proceedings of the Annual Conference of the European Association for Computer Science Logic (CSL-99)*, LNCS, pages 307–321, Springer, Berlin, 1999.

- KS90. P.C. Kanellakis and S.A. Smolka. CCS expressions, finite state processes, and three problems of equivalence. *Information and Computation*, 86:43–68, 1990.

- Kur94. R. Kurshan. Computer-aided Verification of Coordinating Processes: The Automata-Theoretic Approach. Princeton University Press, 1994.

- LBBO01. Y. Lakhnech, S. Bensalem, S. Berezin, and S. Owre. Incremental verification by abstraction. In Margaria and Yi [MY01], pages 98–112.

- LGS<sup>+</sup>95. C. Loiseaux, S. Graf, J. Sifakis, A. Bouajjani, and S. Bensalem. Property preserving abstractions for the verification of concurrent systems. *Formal Methods in System Design*, 6:11–44, January 1995.

- LT88. Kim G. Larsen and Bent Thomsen. A modal process logic. In 1988 IEEE Symposium on Logic in Computer Science, pages 203–210, Computer Society Press, Washington, 1988.

- Mil71. R. Milner. An algebraic definition of simulation between programs. In *Second International Joint Conference on Artificial Intelligence*, pages 481–489, British Computer Society, London, 1971.

- Mil80. R. Milner. A Calculus of Communicating Systems. Number 92 in LNCS. Springer-Verlag, Berlin, 1980.

- MY01. Tiziana Margaria and Wang Yi, editors. *Tools and Algorithms for the Construction and Analysis of Systems*, number 2031 in LNCS, Springer, Berlin, 2001.

- NK00. Kedar S. Namjoshi and Robert P. Kurshan. Syntactic program transformations for automatic abstraction. In Emerson and Sistla [ES00], pages 435–449.

- NNH99. Flemming Nielson, Hanne Riis Nielson, and Chris Hankin. *Principles of Program Analysis*. Springer, Berlin, 1999.

- Par81. D. Park. Concurrency and automata on infinite sequences. In Peter Deussen, editor, Theoretical Computer Science, number 104 in LNCS, pages 167–183, Springer-Verlag, Berlin, 1981.

- PT87. Robert Paige and Robert E. Tarjan. Three partition refinement algorithms. *SIAM Journal of Computation*, 16(6):973–989, 1987.

- RS99. Vlad Rusu and Eli Singerman. On proving safety properties by integrating static analysis, theorem proving and abstraction. In W. Rance Cleaveland, editor, *Tools and Algorithms for the Construction and Analysis of Systems (TACAS '99)*, number 1579 in LNCS, pages 178–192, Springer, Berlin, 1999.

- SBLS99. K. Stahl, K. Baukus, Y. Lakhnech, and M. Steffen. Divide, abstract, and model-check. In Dams et al. [DGLM99].

- Sti89. Colin Stirling. Comparing linear and branching time temporal logics. In B. Banieqbal, H. Barringer, and A. Pnueli, editors, *Temporal Logic in Specification*, number 398 in LNCS, pages 1–20, Springer-Verlag, Berlin, 1989.

- vBvES94. Johan van Benthem, Jan van Eijck, and Vera Stebletsova. Modal logic, transition systems and processes. *Journal of Logic and Computation*, 4(5):811–855, 1994.

- vG90. R.J. van Glabbeek. *Comparative Concurrency Semantics and Refinement of Actions*. PhD thesis, Free University of Amsterdam/Center for Math. and Comp. Sc., Amsterdam, 1990.

- WC99. Andre Wong and Marsha Chechik. Formal modeling in a commercial setting: A case study. In *FM'99 Formal Methods*, number 1708 in LNCS, pages 590–607, Springer, Berlin, 1999.

# Symmetry Reduction Criteria for Software Model Checking\*

#### Radu Iosif

Computer and Information Sciences Department, 318 Nichols Hall, Kansas State University Manhattan, KS 66502, USA iosif@cis.ksu.edu

Abstract. Symmetry reduction techniques exploit symmetries that occur during the execution of a system, in order to minimize its state space for efficient verification of temporal logic properties. This paper presents a framework for concisely defining and evaluating two symmetry reductions currently used in software model checking, involving heap objects and, respectively, processes. An on-the-fly state space exploration algorithm combining both techniques is also presented. Second, the relation between symmetry and partial order reductions is investigated, showing how one's strengths can be used to compensate for the other's weaknesses. The symmetry reductions presented here were implemented in the dSPIN model checking tool. We performed a number of experiments that show significant progress in reducing the cost of finite state software verification.

#### 1 Introduction

The increasing complexity in the design of concurrent software artifacts demands new validation techniques. Model checking [4] is a widespread technique for automated verification of concurrent systems that has been recently applied to the verification of software. Unfortunately, the use of model checking tools [13] is often limited by the size of the physical memory, due to the state explosion problem. In order to deal with this problem, various reduction techniques have been proposed in the literature. Among those, symmetry reductions [3], [8] and partial-order reductions [10], [22] have gained substantial credibility over the past decade. Both techniques are automatic and can be applied on-the-fly, during model checking. The reduction achieved can be significant, in the best cases exponential in the size of the state space.

Symmetry reductions exploit the structure of states in order to identify symmetries that occur during verification. The intuition behind these strategies is

<sup>\*</sup> This work was supported in part by NSF under grant CCR-9703094, by the U.S. Army Research Laboratory and the U.S. Army Research Office under agreement number DAAD190110564, and from the Formal Verification of Integrated Modular Avionics Software cooperative agreement, NCC-1-399, sponsored by Honeywell Technology Center and NASA Langley Research Center.

D. Bošnački and S. Leue (Eds.): SPIN 2002, LNCS 2318, pp. 22-41, 2002.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2002

that the order in which state components (processes, objects) are stored in a state does not influence the future behavior of the system. That is, the successors of two symmetric states are also symmetric. Many criteria have been proposed to decide whether two states are symmetric on-the-fly, without any information about the future states. They usually exploit the ordering of processes [6], communication channels and the structure of temporal logic formulas used to express correctness requirements [8]. Ideally, the reduced state space will have only one state representing each symmetry equivalence class. Unfortunately, detecting all symmetries usually requires very expensive computations, that may make such reductions impractical.

Partial order reductions exploit the commutativity of concurrent transitions, which result in the same state when executed in different orders. The decision whether two transitions are independent, so that they can be safely swapped, is usually made using compile-time static analysis. In practice, this information is a conservative approximation of the real run-time independence. As in the case of symmetry reductions, using more information about the system helps detecting more independence, however it is computationally more expensive. It has been shown [7] that symmetry and partial order reductions are orthogonal strategies and can be used in combination to achieve better verification results.

The main contribution of this paper is applying both techniques to a particular class of software, namely dynamic programs, for which the number of state components (processes, objects) is continuously modified as a result of their ongoing execution. This concept can be used to formalize the semantics of most high-level object-oriented programs, such as the ones written in Java or C++. We show how existing reduction techniques can be specialized to exploit the dynamic nature of software systems in order to achieve more effective verification results.

The present paper is, to some extent, the continuation of our work reported in [19]. There we presented a canonical symmetry reduction that applies only to the heap of the program. Here we combine the heap symmetry reductions with more traditional approaches, such as process symmetries [6]. We first define a framework that allows us to express both reductions formally and compare their efficiency, in terms of canonical properties. Then we describe an explicit-state exploration algorithm that combines heap with process symmetry reduction onthe-fly. Finally, we investigate further optimizations by relating heap symmetries with partial order reductions. Preservation of temporal logic properties is discussed throughout the paper. A prototype implementation of the ideas described in this paper has been done in dSPIN [17], an extension of SPIN [13], especially designed for software model checking. We performed a number of experiments on two non-trivial test cases in order to obtain a practical assessment of our ideas.

#### 1.1 Related Work

Among the first to use symmetries in model checking were Clarke, Filkorn and Jha [3], Emerson and Sistla [8] and Ip and Dill [20]. These approaches consider

systems composed of a fixed number of active components (processors) [3], variables of a special symmetry-preserving data type (scalarset) [20] as well as symmetries of specifications [8]. Using sorting permutation to reduce the complexity of representatives computations has been addressed by the work of Bosnacki and Dams [6]. The problem of exploiting heap symmetries in software model checking has been informally addressed by Visser and Lerda in [21]. To our knowledge, they are the only other group that have addressed heap symmetries to date. Their approach looks attractive due to its simplicity, but no formal evidence of its canonical properties has yet been provided by the authors.

#### 2 Preliminaries

In this section we present some background notions regarding symmetry. The classical framework [3], [8] starts from the basic notion of group of automorphisms in order to define symmetry as an equivalence between states. Since automorphisms preserve graph structure, it can be shown that the symmetry induced by a group of automorphisms is a bisimulation in the sense of Milner [12]. It is therefore possible to define a quotient structure in which each state is a (representative of a) symmetry equivalence class. Model checking the reduced structure preserves all properties that can be expressed using temporal logics [4].

Unfortunately, applying this framework directly to software model checking faces the difficulty of giving the automorphisms appropriate semantic definitions. Indeed, when considering a program in which the number of state components (such as objects or threads) may experience an unbounded growth along an execution path, one cannot consider only one group of permutations as the group of system automorphisms. Instead, we consider a (possibly infinite) family of such groups and chose one at each step, by keeping track of the number of components in every state.

Let  $G_n$  denote the set of all permutations on the set  $\{1,\ldots,n\}$ . It is easy to see that  $G_n$  forms a group with function composition, inverse and the identity mapping as neutral element. Formally, we represent program executions by an (augmented) Kripke structure  $K = (S, R, L, \mathcal{N})$  over a set of atomic propositions  $\mathcal{P}$  and a set of actions  $\Sigma$ , where:

- -S is a set of states,

- $-R \subseteq S \times \Sigma \times S$  is a transition relation,

- $-L: S \to 2^{\mathcal{P}}$  is a function that labels states with sets of atomic propositions,

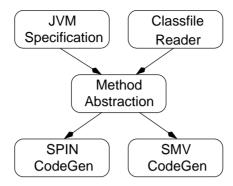

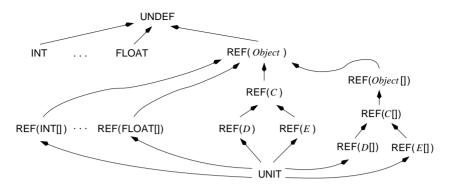

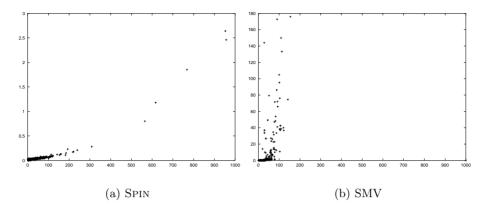

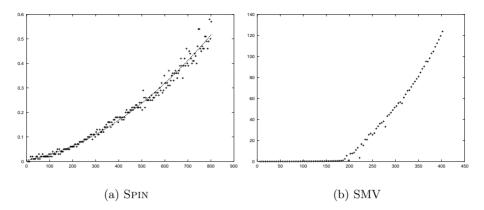

- $-\mathcal{N}$  is a family of functions  $\eta_{\tau}: S \to \mathbf{IN}$ , where  $\eta_{\tau}(s)$  is the number of components of type  $\tau$  occurring in state s.